Concorrência

De Aulas

Afluentes: Sistemas Operacionais, Sistemas Distribuídos e Mobile

Introdução

- Possibilidade de periféricos e dispositivos funcionarem simultaneamente junto com a CPU permitiu execução de tarefas concorrentes.

- Sistemas Operacionais podem ser vistos como um conjunto de rotinas que executam concorrentemente de uma forma ordenada

- Sistemas multiprogramáveis X baixa utilização dos recursos do sistema.

- Uso Médio CPU – monoprogramáveis 30% X multiprogramáveis 90%.

- Vários programas podem estar residentes na memória, deixando-a menos ociosa

- Quando um programa perde o uso do processador, o estado do processamento deve ser armazenado para quando ele retornar para continuar executando a partir de onde parou.

- Compartilhamento de periféricos e recursos do sistema por vários usuários e programas.

- Maior compexibilidade do Sistema Operacional.

Interrupção e Exceção

Interrupção X Exceção

- Interrupção gerada por evento síncrono e Exceção gerada por evento assíncrono.

- Evento síncrono: Resultado direto da execução do programa corrente e são previsíveis.

- Evento assíncrono: Ocorre independentemente da execução do programa corrente e são imprevisíveis.

Interrupções

- Tornou possível a implementação da concorrência nos sistemas multiprogramáveis.

- Eventos que causam intervenção no Sistema Operacional durante a execução de programas.

- Gerados pelo próprio Sistema Operacional ou por Hardware.

- O sistema é desviado para uma rotina especial de tratamento.

- Vetor de Interrupção: Relação de todas as rotinas de tratamento das interrupções.

- Mecanismo de Interrupção: Procedimento para detectar a interrupção, salvar o contexto do programa e desviar para a rotina de tratamento. Na maioria das vezes implementados pelos projetistas e realizados pelo harware.

- Mascaráveis (podem ser desabilitadas) X Não-Mascaráveis (tratamento obrigatório).

- As interrupções possuem prioridades de execução.

- Controlador de pedidos de interrupção – avalia as interrupções geradas e suas prioridades de atendimento.

Exceções

- Resultado direto da execução de uma instrução do próprio programa (ex: divisão por zero, overflow).

- Muitas vezes pode ser escrita pelo próprio programador, sendo possível evitar que um programa seja encerrado no caso de alguma exceção ocorrer.

Operações de Entrada/Saída

Instruções de entrada/saída

- Primitivo.

- Comunicação entre a CPU e os periféricos controladas por um conjunto de instruções especiais.

- Limitava a comunicação do processador a um conjunto particular de dispositivos.

Controlador de Interface

- Mais atual

- CPU interage independente dos dispositivos de E/S.

- CPU não comunica diretamente com periféricos, mas atravéz de um controlador.

- Controle de operações de E/S pelo processador

Controlada por programa

- CPU sincronizada com periférico no início daoperação

- Sistema testa periférico esperando final da operação

- Ocupa CPU até término da operação (busy wait)

- Desperdício de CPU.

Por Polling

- CPU liberada para outras tarefas.

- Controlador testa final da operação a cada período de tempo (polling).

- Permitiu o paralelismo e sistemas multiprogramáveis.

- Mais eficiente

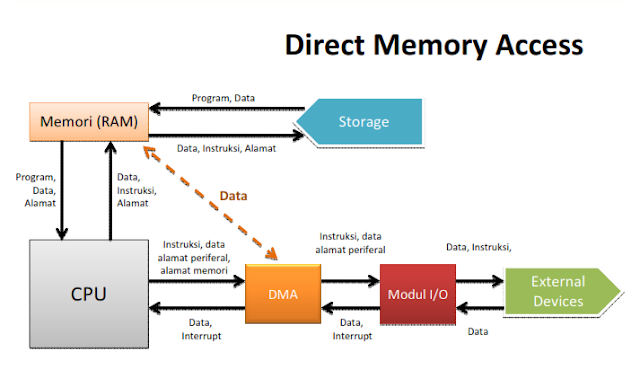

Direct Memory Access (DMA)

- Polling exigiu a implementação, por parte do controlador, da Direct Memory Access (DMA).

- Transferir blocos de dados entre memória e periféricos, sem intervenção da CPU, a não ser no início e término da operação.

- CPU interrompida só no início e final da Operação.

- No momento da Transferência da DMA, CPU interrompe acesso ao bus.

No IBM 7094

- Extensão do conceito de DMA

- Canal de E/S – processador para executar programas de E/S.

- Controle total sobre operações de entrada e saída.

- Instruções E/S armazenadas na memória principal pela CPU

- CPU instrui canal para executar programa de canal.

- O canal avisa o término da operação.

- Um canal pode controlar múltiplos dispositivos através de diversos controladores.

- Um controlador pode manipular um dispositivo, ou um conjunto de dispositivos.

- Canal - ligação entre CPU e controlador.

Processador de E/S

- Evolução com memória própria.

- Sem necessidade de programas de E/S serem carregados na Memória Principal.

- Controle com mínima intervenção da CPU.

Buffering

- Utilização de uma área da memória para transferência de dados entre periféricos e memória principal denomidada buffer.

- Os dado são transferidos para o buffer.

- O dispositivo pode iniciar nova leitura enquanto a CPU manipula os dados do buffer.

- O mesmo pode ser aplicado para operações de gravação.

- Minimiza o problema da disparidade da velocidade de processamento e dispositivos de E/S

- Objetiva manter CPU e dispositivos de E/S ocupados na maior parte do tempo.

- O buffer possui uma fila FIFO podendo conter vários registros (unidade de transferência usada no mecanismo de buffering).

Spooling (simultaneous pefipheral operation on-line)

- Surgiu no final dos anos 50.

- Base dos Sistemas Batch

- Antes, as Operações I/O eram lentas, deixando a CPU ociosa.

- No spooling vários programas (JOBS) eram armazenados em uma fita magnética, então eram enviados para processamento.

- Diminuição do tempo de execução dos jobs e transição entre eles.

- Da mesma forma um job poderia direcionar as saídas para impressora para outra fita.

- Sistemas estritamente sequenciais devido as fitas magnéticas.

- Mais eficiência com o surgimento de dispositivos de acesso direto, como discos e atribuição de prioridades aos jobs.

Reentrância

- Diversos usuários podem estar rodando o mesmo utilitário (compartilhado) simultaneamente.

- Não precisa ter mais de uma cópia do mesmo utilitário na memória

- Exige que o código reentrante não possa ser modificado por nenhum usuário enquanto está sendo executado.

- Diversos usuários podem acessar partes diferentes do código manipulando seus próprios dados

- Exemplo: Editores de texto, compiladores, linkers.

Proteção do Sistema

- Garantia de proteção de recursos compartilhados, como memória, dispositivos de E/S e CPU

- Na memória, cada usuário deve possuir uma área de dados e códigos armazenados de forma que outros não interfiram nessas informações.

- Numa impressão, não deve ser possível a utilização até que a impressão corrente termine.

- O Sistema Operacional deve implementar esses mecanismos (modos de acesso).

Lista de Exercícios

- Defina Sistemas Multiprogramáveis e cite suas principais características.

- Diferencie Interrupções de Exceções.

- Descreva o mecanismo de interrupção.

- O que é controlador de interface e diferencie o controle de operações de E/S controlada por programa e por polling.

- Cite algumas características que apareceram com o surgimento do DMA, com o IBM 7094 e o Processador de E/S.

- O que é a técnica buffering em relação ao Sistema Operacionais e dispositivos, qual a função do buffer e como funciona?

- Defina a técnica de Spooling em relação aos Sistemas Operacionais e dispositivos.

- Explique o que é a Reentrância, cite e explique alguns exemplos.